### EDSAC in Verilog

Bill Purvis, September 2017 EDSAC Replica Project

### Initial Task: Reconstruct and Validate Logic

Starting point: Edsac Report - 1948

Mostly text, few diagrams

Computer

Conservation

Society

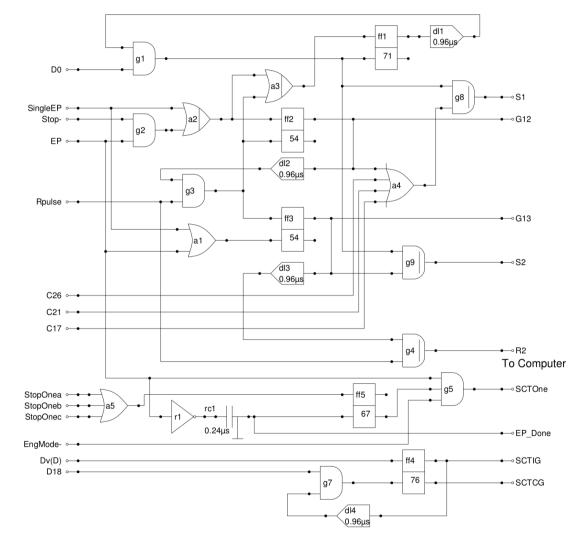

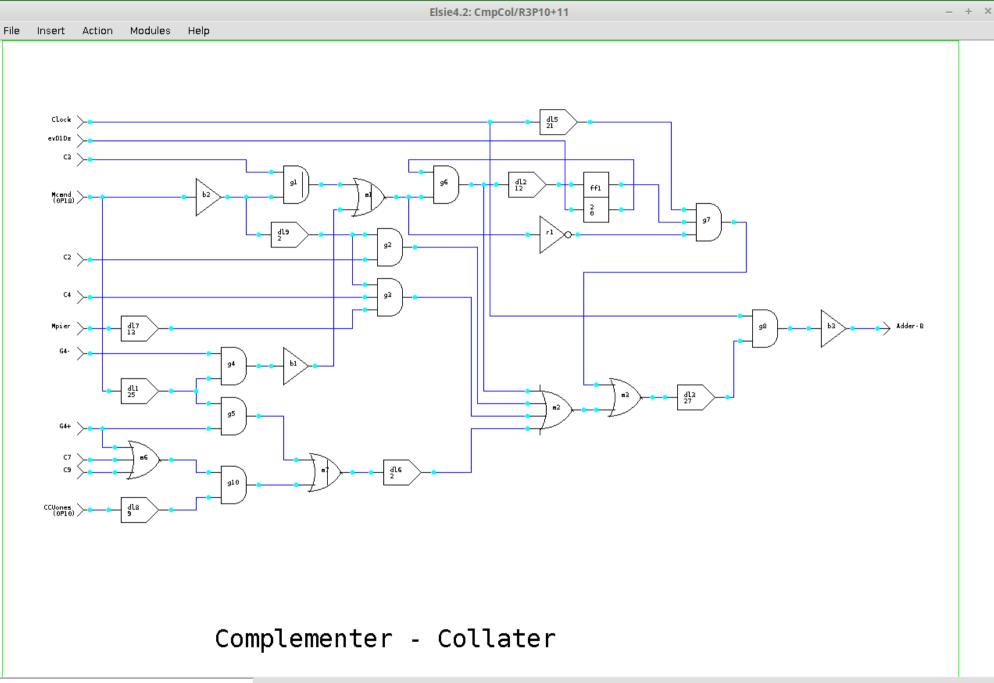

### Redraw using a home-grown Logic Editor - ELSIE

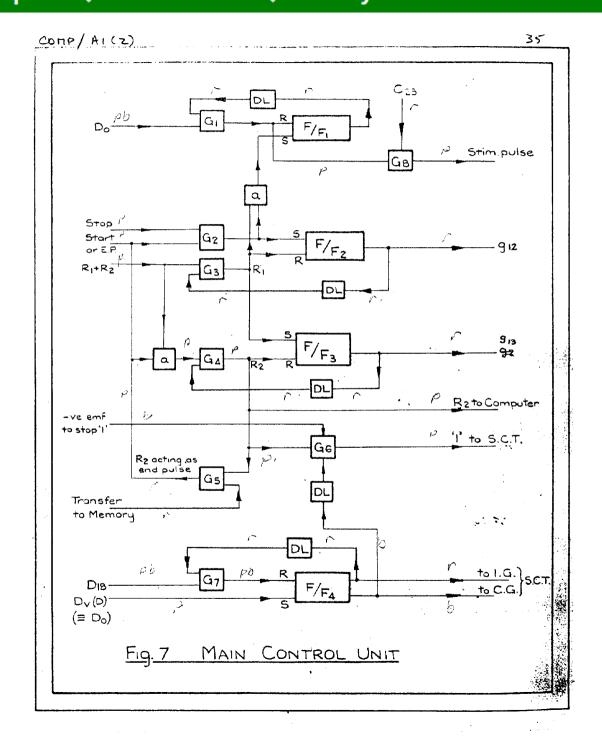

MAIN CONTROL UNIT

Computer

Conservation

Society

### Next step: Simulation

### ELSIE simulates EDSAC devices

```

Time step fixed at 80nSec,

25 time steps = 1 EDSAC clock pulse

```

CCS Computer

Conservation

Society

|                                                                                        |              |                 | Elsie                     | e4.2: Scope Traces                            | : test8a: muladd | + +      |          |          |         | - + ×           |

|----------------------------------------------------------------------------------------|--------------|-----------------|---------------------------|-----------------------------------------------|------------------|----------|----------|----------|---------|-----------------|

| 9216us 128c 127C1                                                                      | P23 pulse Ad | der-Sum @ 131C1 | 4P14 w <b>d</b> 1614 ht ( | 0%                                            |                  |          |          |          |         |                 |

| MCU/M1P8+9+10.S1.A                                                                     |              |                 |                           | 1                                             |                  |          |          | 1        |         |                 |

| MCU/M1P8+9+10.S2.A                                                                     |              |                 |                           | 1                                             |                  |          |          |          |         |                 |

| CU/M2P10.Rpulse.A                                                                      |              |                 |                           |                                               |                  |          |          |          |         |                 |

| MCU/M1P8+9+10.R2.A                                                                     |              |                 |                           |                                               |                  |          |          |          |         |                 |

| CCU6/R5P8.EP.A                                                                         |              |                 |                           |                                               |                  |          |          |          |         |                 |

| MCU/M1P8+9+10.G12.A                                                                    |              |                 | l                         |                                               |                  |          |          |          |         |                 |

| MCU/M1P8+9+10.G13.A                                                                    |              |                 |                           |                                               |                  |          |          |          |         |                 |

| CU/M2P10.CG+.A                                                                         |              |                 |                           |                                               |                  | 7        |          |          |         |                 |

| XFR/M1P12.MOB.A                                                                        |              |                 |                           | Л.ШШ.Л                                        |                  |          |          |          |         |                 |

| XFR/M1P12.MIB.A                                                                        |              |                 |                           |                                               |                  |          |          |          |         |                 |

| Ctr/M1P2.Counter.A                                                                     |              |                 |                           |                                               |                  |          |          |          |         |                 |

| SCT/M2P11.SCT.A                                                                        | _1           |                 |                           |                                               |                  |          | _MN      | 1 1      | N       |                 |

| Order/M2P11.Order~.A                                                                   |              |                 |                           | <u>, , , , , , , , , , , , , , , , , , , </u> |                  | 1 7771 1 |          | 1.0001.0 |         |                 |

| Acc/R4P4.Acc1.A                                                                        |              |                 |                           |                                               | N <b>IIII</b> N  |          |          |          |         |                 |

| Acc/R4P4.Acc2.A<br>ASU2/R3P2.Adder-A.A                                                 | _\           |                 | Λ ΙΙΙΙ Λ                  |                                               |                  |          | N IIII N |          | NIIII_N |                 |

| CmpCol/R3P10+11.Adder-B.                                                               | ۵            |                 |                           |                                               |                  |          |          |          |         |                 |

|                                                                                        |              |                 |                           |                                               |                  |          |          |          |         |                 |

|                                                                                        |              | n <b>IIII</b> n |                           | n <b>IIII</b> n                               |                  | 0.000    |          | 0 1111 0 |         | N <b>IIII</b> N |

| Adder/R3P8.Adder-Sum.A                                                                 |              |                 | 100                       |                                               | 100              |          | 100      |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A                                          | LM           | NUU_/           | 10                        |                                               | IM               |          | LM       |          | LAN     |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A                  |              |                 | 110                       |                                               | 10               |          | 10       |          | 100     |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 | 100                       |                                               | LUI              |          | 100      |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A                  |              |                 | 100                       |                                               | 1.1.1            |          | 1.00     |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 | 110                       |                                               | 110              |          | 100      |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 | 110                       |                                               |                  |          | IN       |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 |                           |                                               |                  |          | 1.N.     |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 |                           |                                               |                  |          |          |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 |                           |                                               |                  |          |          |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 |                           |                                               |                  |          |          |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 |                           |                                               |                  |          | IN       |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 |                           |                                               |                  |          |          |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 |                           |                                               |                  |          |          |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 |                           |                                               |                  |          |          |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 |                           |                                               |                  |          |          |          |         |                 |

| Adder/R3P8.Adder-Sum.A<br>Mpier/R4P11.Mpier.A<br>Mcand/R4P13.Mcand~.A<br>TCT/R4P6.Dx.A |              |                 |                           |                                               |                  |          |          |          |         |                 |

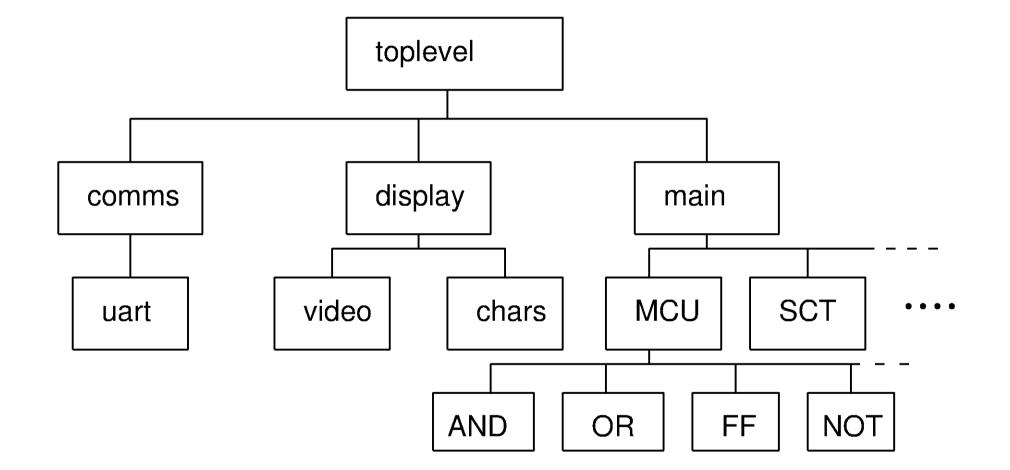

### Gate-level simulation, very slow!

Run very short test programs

# Sufficient to establish confidence that the logic should work

Used as a basis for detailed circuit design

Suggestion that a Verilog implementation might be useful

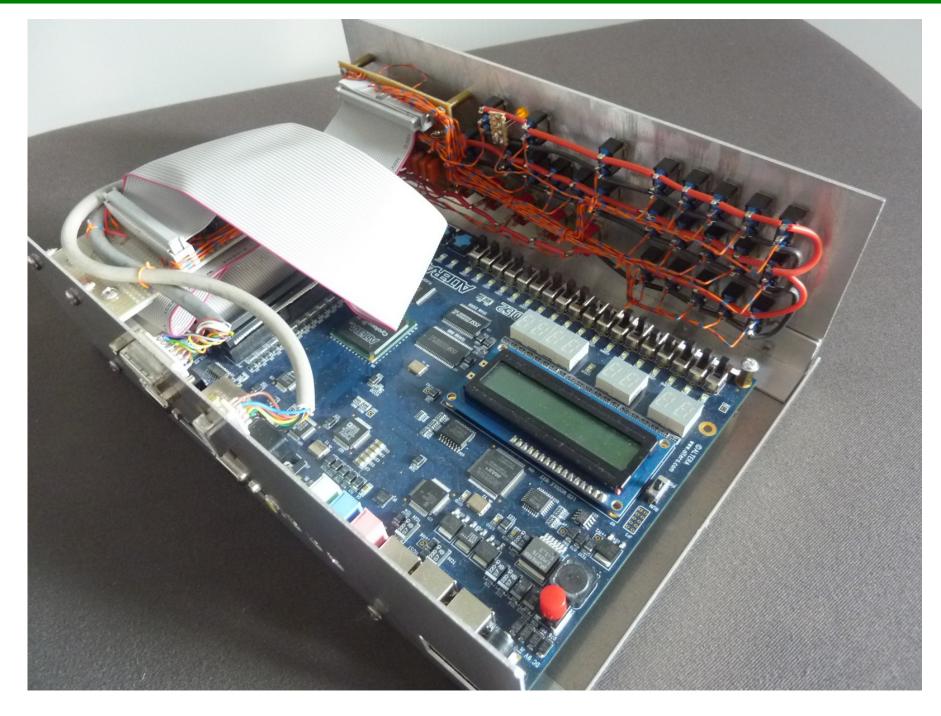

Offer of Altera DE2 development board (Simon Moore, Cambridge University)

Modify ELSIE to export suitable Verilog code

Hand code Verilog to simulate EDSAC elements and ancilliary modules for I/O and display.

Build board into case with switches etc.

## **CCS** Computer **♦** Conservation **♦** Society

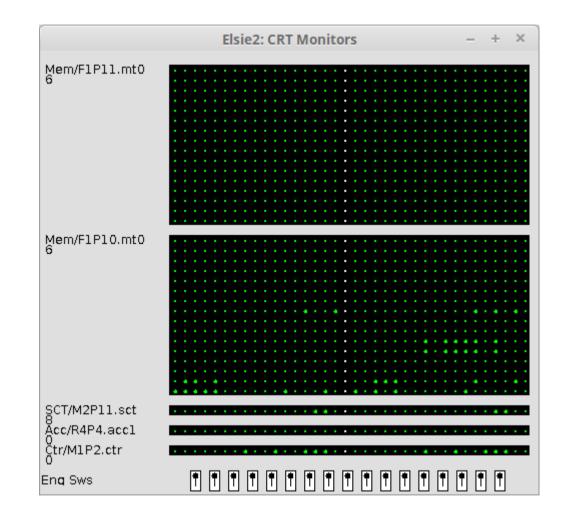

RS232 link to PC/Raspberry Pi for virtual I/O devices:

Virtual Paper Tape Reader

Virtual Teleprinter

SVGA port for memory/register displays

Real tape reader added

Real teleprinter still pending

### Reimplenting with Altera DE2-115 board

Bigger FPGA, Touch Screen

Work in progress, display, button, but no VIO yet

### Mini-EDSAC

- Initial version for IceStick

- Reduce to 16-bit architecture (from 35-bit)

- Simplify some orders

- Switch to ASCII tape coding

- Register-level coding, not gate-level

- Parallel not serial!

- Migrate to BlackIce board

- Needed external UART for RS232

Project proposal 1:

Extend order set to implement B-register extension One additional register Three additional orders

Project proposal 2:

Extend to full EDSAC simulation:

Two orders (17-bit) per word (35-bit)

Original order set

Serial arithmetic??

### Links:

## http://www.billp.org/EDSAC http://www.billp.org/FPGA